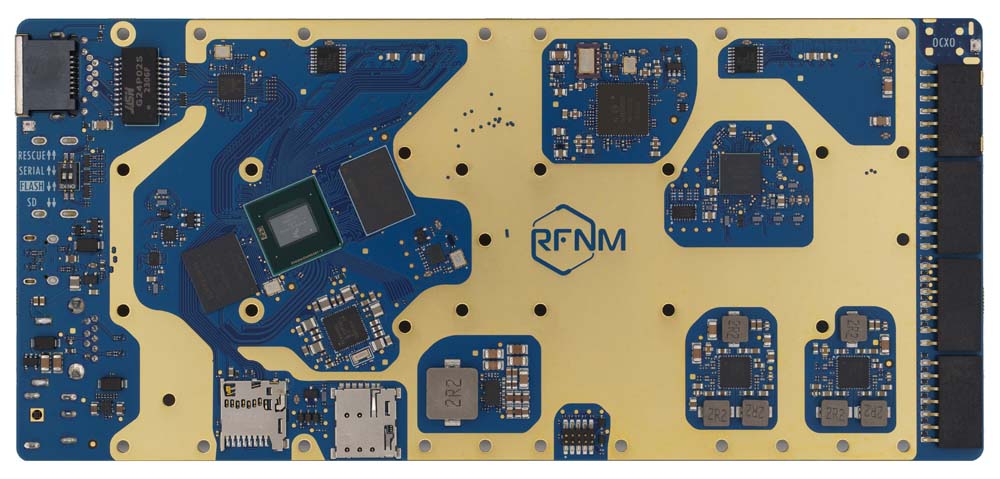

Appearance

RFNM Motherboard

The RFNM motherboard is a new concept, so it's worth taking a few seconds to understand it.

In a nutshell, the most complicated parts are consolidated into a single block, the motherboard, and all of the interesting and fun bits are exposed via the RFNM Interface to daughterboards.

What is packed into this motherboard are the common components required for many different applications, such as:

- Software Defined Radios

- Signal Generators

- Oscilloscopes

- Anything requiring good ADCs/DACs and clocking/timing

What is included in the motherboard

LA9310

The smallest brother of the NXP Layerscape series. This beautiful ADC/DAC comes with a powerful embedded DSP core and a 8 Gbps host interface.

The LA9310 was only accessible through a paid Access Agreement before being released in the RFNM motherboard.

- 4x differential ADC I/Q pairs; 8x differential ADCs when used individually.

- 1x differential DAC I/Q pair; 2x differential DAC when used individually.

- VSPA-16SP DSP core running at 614 MHz with ~80 GFLOPS of power. On paper, this is a small monster that can compete with what is used inside the DJI FPV system.

- 32 kB data memory, enough to perform 2k-wide FFT on the fly or 4k-wide blocking. Program memory can be swapped in/out extremely fast via the PCIe interface.

- 307 MHz Arm M4 coprocessor.

- DSP toolchain purchasable from NXP for ~3k (Codewarrior VSPA Software Professional Edition).

- Baseband (ADC/DAC) frequency of either 122.88 MHz or 153.6 MHz.

Si5510

This is a timing chip from Skyworks that is also just now reaching the release stage and is still under NDA.

It provides coherent, low jitter clocks to everything on the board that would benefit from them, has an optional external MMCX input and a numerically controlled oscillator that we can adjust down to 1-ppt for exact frequency adjustments.

- Ultra low jitter and phase noise (exceeds 5G specs), -145 dBc/Hz @ 1 MHz, < 45 fs typical jitter.

- 18 differential outputs, with each daughterboard slot having two dedicated clocks.

- 280 ppb TCXO.

- External MMCX input and output clocks for chain synchronization.

- Differential output clock going off board (not to the daughterboards).

- Integer output clocks up to 3.2 GHz and fractional up to 650 MHz.

- One part per trillion numerically controlled oscillator to adjust the TCXO or external input frequency to a reference standard.

i.MX8M Plus

The i.MX8M Plus onboard processor has the same CPU as the Raspberry Pi 3 Model B (Quad Core Cortex A-53), but is clocked slightly faster at 1.6 GHz vs 1.2 GHz. This is your usual, modern and fast embedded processor, but it being supported by NXP, it will receive kernel updates for a long time to come.

- 4x 1.6 GHz Cortex A-53 cores for onboard applications or data processing.

- HDMI 2.0, 4k @ 30fps for data visualization and onboard applications.

- 2x USB 3.0 ports that can be used to stream data extremely fast, up to the point of saturation for the LA9310 PCIe interface.

- 1 Gbps ethernet interface with TSN (Time Sensitive Networking)

- 4 GB LPDDR4 and 64 GB of eMMC storage.

- USB-C with power delivery (sink) and a Micro-SD interface.

- 16 GFLOPS GPU with OpenGL/CL and Vulkan.

- Real Time Coprocessor: Cortex-M7 @ 800 MHz.

SN220E

The SN220E is a secure enclave (e-SIM) that can, in theory, be used to enable the RFNM ecosystem as a 5G RedCap node, allowing it to connect to the next generation of networks being deployed around us. This is only possible thanks to the advanced characteristics of chips in the motherboard, that meet the 5G specs, and the processing power of the VSPA DSP and Cortex A-53 cores that allow it to be a full, independent and autonomous node on a real network.

User Interface

Not to be confused with the RFNM daughterboard interface, this is a series of 2.54mm/0.1" pitch headers on the side of the board that you can think of like an Arduino header. Unlike an Arduino, we also have PPS in/out signals and differential clocks mixed in there.

Multiplexers and Latches

Finally, these are the least technologically advanced ICs onboard, yet, they cover a very important detail with radio frequency frontends: You need to switch to the right signal path, or turn off the correct power amplifier, at the exact time that is required by the protocol you are implementing (and those numbers can get pretty tight).

As a simple example, in a TDD system (time-division multiplexing), we might need to switch between receive and transmit signal chains every few milliseconds, with sub-millisecond accuracy. If a power amplifier is involved, not frying the receiver usually also implies making absolutely certain that the PA has had the time to cool down before you reconfigure the switches.

To add to the complication, daughterboards such as the Granita have in the order of 100 different GPIO pins that needs to be configurable with the tightest tolerances possible, and it all needs to be synchronized with the baseband clocks.

The system of logic ICs we implemented allows us to do just that.

Oscilloscope example proves ecosystem flexibility

For example, consider what is required to build an oscilloscope, which is something the motherboard was not designed to support:

- Fast ADCs. We have 8x 12-bit, 153 MSPS ADCs onboard.

- A good timing chip. Not very important at those frequency, but we can check that box.

- Fast interfaces for streaming data. All of the ADCs combined can theoretically stream at up to 8 Gbps over the PCIe 3.0 1x interface, and we verified this to work reliably to at least 4 Gbps.

- A triggering mechanism to limit data bandwidth, that can be provided either at the source (the DSP inside the LA9310 ADC chip) or between the source and the user (the i.MX).

- A user interface method, which can be via the embedded HDMI port, or from a host PC connected to the USB 3.0 interface.

All of the above, the complicated parts, are provided by the motherboard. The simple bits, such as the analog conversion of a low bandwidth signal for input to the ADC, would be handled by a specific oscilloscope daughterboard.

This way, most of the complexity in adding a new function to the ecosystem is abstracted away. Anyone can build a simple analog board for the oscilloscope application.

Current development status

Fully verified and ready for manufacturing.